March 2011

Integrated Circuit Design-Lab1Question

Swinburne

University of Technology

Faculty of Engineering

and Industrial Sciences

HET378 Integrated Circuit Design

Mini-Project

1

Hardware modeling

Design of a

Basic ALU

Laboratory

Part

1 : Hardware Modelling

Write

a VHDL source code that implements the hardware of the sequencer shown below.

Synthesize your source code and compare the results to the circuit.

(Your

objective is to reproduce the same circuit . Simulation is not required)

Fig 1

Part

2

Design

and Implementation of a

This lab design

project which gives you more freedom to come up with your own solutions. The

following write-up serves as a guideline to help you design the lab. However,

if you find more efficient or more elegant ways to implement parts of the ALU,

go ahead. Just make sure you justify your design and explain it clearly in the

lab report write-up.

Pre-laboratory work:

Do the pre-lab4-bit

ALU work for part 2

An Arithmetic and Logic Unit (ALU) is a combinational circuit that performs logic and arithmetic micro-operations on a pair of n-bit operands. The operations performed by an ALU are controlled by a set of function-select inputs. In this lab you will design a 4-bit ALU with 3 function-select inputs: Mode M, Select S1 and S0 inputs. The mode input M selects between a Logic (M=0) and Arithmetic (M=1) operation.

A block

diagram of the ALU is given in Figure 2.

Figure 2: Block diagram of the 4-bit

ALU.

The functions performed by the ALU are specified in Table I.

Table 1: Functions of ALU

|

||||

M = 0 Logic

|

||||

S1

|

S0

|

C0

|

FUNCTION

|

OPERATION

(bit wise)

|

0

|

0

|

X

|

AiBi

|

AND

|

0

|

1

|

X

|

Ai

+ Bi

|

OR

|

1

|

0

|

X

|

AiÅ Bi

|

XOR

|

1

|

1

|

X

|

(AiÅ Bi)’

|

XNOR

|

M = 1 Arithmetic

|

||||

S1

|

S0

|

C0

|

FUNCTION

|

OPERATION

|

0

|

0

|

0

|

A

|

Transfer

A

|

0

|

0

|

1

|

A + 1

|

Increment A

by 1

|

0

|

1

|

0

|

A + B

|

Add A and B

|

0

|

1

|

1

|

A + B +

Carry in

|

sum of A

and B and Cin

|

1

|

0

|

0

|

A + B'

|

A plus

one's complement of B

|

1

|

0

|

1

|

A - B

|

Subtract B

from A (i.e. B' + A + 1)

|

1

|

1

|

0

|

A' + B

|

B plus

one's complement of A

|

1

|

1

|

1

|

B - A

|

B minus A

(or A' + B + 1)

|

Note that

the zero and Carry flag are cleared for logical operation and are affected by

the arithmetic operations

This design project gives you freedom to come up with your own solutions. The following write-up serves as a guideline to help you design the ALU. However, if you find more efficient or more elegant ways to implement parts of the ALU, go ahead. Just make sure you justify your design and explain it clearly in the lab report write-up.

When doing arithmetic, you need to decide how to represent negative numbers. As is commonly done in digital systems, negative numbers are represented in two’s complement. This has a number of advantages over the sign and magnitude representation such as easy addition or subtraction of mixed positive and negative numbers. Also, the number zero has a unique representation in two’s complement.

Design

strategies

There are

different ways to design the ALU. One method consists of writing the truth

table for the one-bit ALU. This table has 6 inputs (M, S1, S0, C0, Ai

and Bi) and two outputs Fi and Ci+1. This can

be done but may be tedious when it has to be done by hand.

An

alternative way is to split the ALU into two modules, one Logic and one

Arithmetic module. Designing each module separately will be easier than

designing a bit-slice as one unit. A possible block diagram of the ALU is shown

in Figure 2. It consists of three modules: 2:1 MUX, a Logic unit and an

Arithmetic unit.

Fig 2

A third

option is design the ALU using modular STD_logic functions

Laboratory work

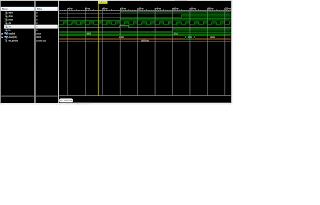

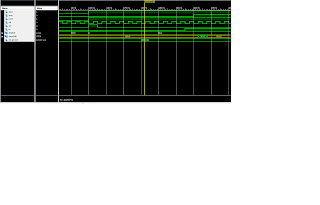

(1) Your task is to design and implement

the 4-bit ALU using the Xilinx Foundation and Modelsim tools. Follow the guidelines of the pre-lab in designing the 4-bit ALU.

Develop two models for the ALU, and use Xilinx and Modelsim tools to

simulate and synthesise the design

(2) Extend the design to a 16-bit ALU

Hand-in

You have to hand in a lab report that

contains the following:

- Synthesis results for part 1

- VHDL code (design and test

bench), simulation and synthesis results for part 2

- Conclusion and discussion

The lab report is an important part of

the laboratory. Write it carefully, be clear and well organized. It is the only

way to convey that you did a great job in the lab.

Ismat Hijazin

March 2011